#### UNITI

#### DIGITAL SIGNAL PROCESSORS

o What is pipolining? what are the diperent stages in pipelining?

The pipelining netons to everlapping of execution of various phases of different instructions so that a number of instructions can be executed in parallel. There are four stages in pipelining.

- 1. The fetch phase

- 2. The desde phase

- 3. Hemory nead phase

- 4. The exerte phase

2) what is the function of parallel boil unit?

The parallel logic unit is a second logic unit that execute logic operations [ANID, OR, XOR, etc] on data without affecting the content of accumulators.

write any two applications of Exp:-

- 1. Digital cell phones.

- 2. Automated insportion

- 3. Video conjerening

- 4 Noise carrellation

- 5. Medical imaging

- 6. Satelite communication

A How do a digital rignal processor differ from other processon? what are the special jeathores of digital rignal processon?

The special beatures of digital vigital processor

ase

- 1. Fast dota alless

- 2. Fast computation

- 3. Numerical pidelity

- 4. Fast execution control

- 5. List the addressing males of 7m5 320050 DSP

- 1. Dinect addressing 2. Memory mapped register addressing 3. Indinect addressing 4. Immediate addressing 5. Dedicated negister addressing 6. Circular addressing.

- Hention one impostant feature of Harmand

insultancons alless of instruction and data is a single cycle. Tied two marrony alless in one yells.

I what is an advantages of pipelining?

instruction is possessmed one by one (ie) after complete execution of an instruction the next instruction is fetched from memory.

In pride your with pipelining, the instruction execution is divided into various phase / stage and accusion of different phase of the on mone instructions are paryound is passallel.

So that computation time is law.

- 8. List the various negisters used with ARAU:-

- 1. Eight Auxiliary registers (ARO-ARF)

- 2. Auxiliary register pointer

- 3. Uningued 16-bit ALU.

- 9. What are the different Bruses of TMS 3205542 processor and list their functions:-

- 1. Program Bus.

- 2. program Addien Bw.

- 3. Data spead BW.

- 4. Data read address Bus.

### Function: -

- 1. The program bus various the instruction ade and immediate operand from program memory, to the CPV.

- 2. The payan address bus parides address to program memory space for both read and write. 3. The data need bus internments vious

dements of the CPU to data memory space.

4. The data read address Bus provides the address to allers the data memory space.

in what is meant by memory mapped register? The TMS 320 CS47 has 32 numbers of 16-64 CAU registores that are mapped into page - o of data memory space. Those memory mapped negisters included registers on data and program marine memory addrew generation, vacciono status and control negisters to coo and accumulations.

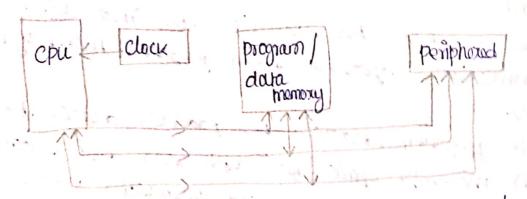

Draw the block diagram ob hardward architecture, von houman architecture and explain.

Von houman Archibertuse:

In 1946, John Von Neuman developed the Power computer anchitecture. In this, Instructions are stored in Read only themony (Roth). The Von Neuman Stored in Read only themony (Roth). The Von Neuman Anchitecture is most widely used in majority of microprocessor.

In a computer with von Neuman architecture, the CPU can be esther reading an instruction on reading whiting a data from to the memory.

Deading and writing can not access at me same time, since the instruction and data we the same signal trainways and memory.

The von nouman conchileture consists of three busy

. w me Data bus

2) Address bus

3) control bus.

The Data bus:

Transport data between cps and Pts persphorals.

It B bidurectional. The cpu can be read or write data in me phoriphorals.

### The address bus:

The cpo user the address but to indicate which peripherals it wants to a case and within each peripheral which specific register.

The dddnors bus is unsubrectional. The copy always where the address, which is road by the perspheral.

#### Control bus:

the exchanges between the you and the performance, as well as that Indicates if the you wants to read on write the performals.

### Di sadvantages of von Newman:

The main demonsts of von Neuman and Its passes only one bus syptem. It passes only one bus syptem. The same bus carries all the inbormation exchanged between the and the photopheraus, including me fruintier was as well as the data processed by the up.

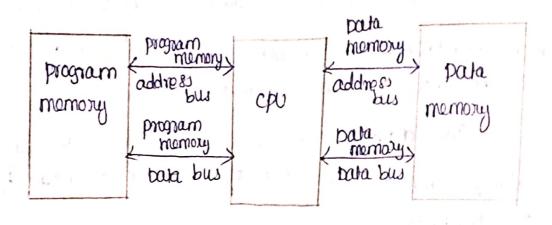

### Honvard anchilleruse:

The horvard archibeture physically separales box theen gristructions and data, recurring memories. deallated buses for each of them. Therefore Instructions and operands can be fetered simultaneously.

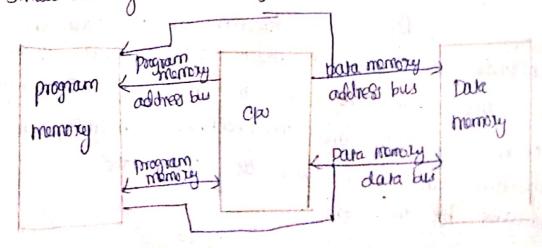

Modelited Honord Anchelouse

In modified horvard archibiture, one memory block is dedicated for storing data alme another memory block box storing Instruction and data. This architecture will also have separale bases to access Instruction and date Simultaneously in one cycle.

### Demont :

The modelised horvard architecture uses reparale this system box program memory and data monoxy and inputs outputs periphonals. It may also have multiple but system there multiple but system there multiple but system increases the "Complexity of the CPU".

### Advantages:

It acress revocal memory location structure outly, Those by Increasing the data throughout between memory and etc.

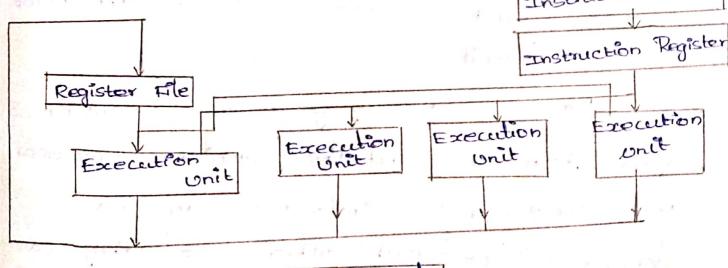

2 Explain the advantages and disadvantages of VLIW anchitecture (Nov | DEC - 2012)

VIIW Means Very long Instruction Word.

anchitecture. In this polocessor Many

Instructions are followed at the same time

and issued to multiple execution, units

to be executed in porallel

Instruction cache

Data Cache

the VIIW processor consists of architectup that leads a orelatively large group of instructions and execute them at same time.

The VIIW powcessor combines Many simple instructions to a single long instruction word that uses different registers.

In VIIW, A language compiles or pre-processor separate the program instructions anto basic operations that are performed by the processor in parallel.

These operations are placed into a "Very long construction word" that the processor can then dix assemble & then transfer each operation to an appropriate execution unit.

For example, the group might contain form Instructions and the compiler ensources that those four instructions are not dependent on each other so they can be executed simultaneously otherwise it

places 'no-ops' (blams instruction) in the group where neccessary.

### Advantages:

- Increased performance.

- -> Botter compiler targets

- -> potentially scalable

- > potentially easier to pregram,

- -> can add more execution Units, allow more instruction to be packed.

### Disadvantages:

- -> New tend of programmer compositer

- -) Program Most keep track of Instruction

sheduling.

- Increased Memory one

- -) High power consumption

- Misleading MIPS stating.

3. What is MAC Unit and pipelining. Explain its functions. MAC Unit (MAY/JUNE - 2014)

The fast computation is digital signal processor is achieved by MAC Unit [multiply / Accumulate Unit]

The popular computation in digital signal poroccossing are FFT, convolution a correlation and so these operations involves multiplication and summation of laythy numerical across.

The MAC Unit in the Cpc of digital signal perocessor is capable of computing one multiplication and addition in a single clock cycle.

Typically a MAC Unit will have a multiplier, a set of sugisters, a slitifer and an AHU.

Example:

The instruction "MACD tym, dmo" Scanned by CamScanner will define that multiply the contents of program memory (pgm) and data memory (dma) specified by instruction and add to the sum of products in the accumulator with appropriate shift in an single class cycle.

Let us consider the output of file file file  $y(n) = \lim_{k=0}^{n-1} \chi(k) h(n-k)$

In the above equation to compute the output, the minimum sugairement is to make it possible, a dast oversult. To make it possible, a fast oversult.

dedicated handware. MAC. Using either diaed point or floating point arithmetic is mandatory.

Typical fixed point MAC Include

- 1. 16x16 bit 2's complement inputs

- 2. 16×16 bit multiplet With 32-bit

producos in 25nc

3. 32/40 bit accumulator.

MAC Functions!

A MAC Unit performs the following

- -> Reads a 16-bit Sample data.

- -) Increment the sample data pointer by a.

- -> Reads a 16-bit co-afficient.

- Therement the Co- efficient su regaister pointer by 2.

- + Sigh multiply (16-bit) data and co-effici.

-ent

a 32 bit sugister pair for accomulate.

The TNS 320 C54 × multiply, accumulate Unit performs a 16 × 16 -> 32 bit fractional multiply - accumulate operation in a single instruction cycle.

The multiplies supports signed/ signed

Multiplication, signed punsiqued multiplication, and punsiqued punsiqued multiplication.

Many Instruction using the MAC unit can optionally specific automatic sound to measurest rounding

Repelining.

The pipelining refers to overlapping of execution of various phases of different instanction so that a number of instanctions can be executed in parallel.

In DSP's the execution of each instruction is divided in 4 or 6 phases. In 4-phase pipelining, when first instruction in 4th phase of execution, the second will be in 3rd phase will be in 2rd phase and fourth will be in 1st phase of execution

The steps in the pipelining are exten called stages. The basic action of any microprocessor pan be broken down into a series of four simple steps. They are 1. The Fetch 3. Menuory need

2. The decode of Execution

Fet ching:

In which the next instruction is fetched from the address stoned in the program counter

Decoding:

In which the instruction in the instruction register is decoded and the address in the program counter is incremented

Memory Read:

It reads the data forom the data buses and also writes the data to the data buses

### Execution.

This phase execute the instruction surrently in the instruction register and also completes the write prouss

Each of the above stages may be carried out seperately by four functional civils

Instruction 1  $f_1 \mid D_1 \mid R_1 \mid X_1 \mid$ Instruction 2 f<sub>2</sub> D<sub>2</sub> R<sub>2</sub> X<sub>2</sub>  $F_3$   $D_3$   $R_3$   $X_3$ Instruction 3  $F_4$   $D_4$   $R_4$   $X_4$ Instauction 4 Pipelining leads to dramatic improvements in system performance. The more pipelining stages, we can get mon speed Explain Narious Addressing modes of a digital Signal Processors. Nov/DEC 2011 ADDRESSING MODES: The Addressing mode is the method If specifying the data to be operated by an but muchion. The DSP praemors support the following Six addressing modes

# 1 Direct Addressing

- 1. Memory Mapped negistes Addressing

- 3 Indirect Addressing

- 4. Immediate Addressing

- 5. Dedicated Register Addrewing

- 6. Circular Addressing

# Direct Addressing.

In direct addressing, the lower 1 bits of data memory address are specified directly in the instruction itself. The upper 9 bits of the address will be the content of data memory page pointer (DP) is status register.

Example:

ADDC 21h [Add the content of data memory where address is specified in the insteach in

Memory Mapped Regista Addressing.

In memory-mapped register addressing the address of the memory-mapped register can be

Specified as direct address in the instruction

EXAMPLE:

LAMM 16h [ Load accumulated with the content of memory snapped to address 0016h.]

Reversed Addressing.

It is a special rose of indirect addressing. In bit hercesed addressing, the data memory address is specified by AR like indirect addressing, but the content of AR is incumented or decemented in order to generate the data memory address in the bit reversed profer, using the content of index register.

MAC 14FOh, \* BRO + St defines & as multiply

the content of program (14Foh)

by the data memory

Hore the data memory is the content of AR currently pointed by ARP. The AR is incommented to great the bit reversed addressed of data memory a Scanned by CamScanner

# IMMEDIATE ADDRESSING:

In indirect addressing mode, The data namony address is specified by the content of one of the eight auxiliary register (ARO-AR7). The AR currently used for accessing data is denoted by ARP (Auxiliary Register pointer)

Example:

Acci, 0; Load the content of data memory

addressed by AR, AR is not altered.

LACE\*+,0: Same as above, but AR is incumented

by ene

LACE\*-,0; Same as above but AR is decumented

by one

SYNTAX BED IN INDIRECT ADDRESS FOR MODIFYINGIAES

Syntax Modification of AR

AR Unaltered

\* AR Incumented by one

\* O+ AR Incumented by the content of Index

Register

\* O- AR Decemented by the content of

Index Registers

\*BRO+ AR Incumented for bit reversed addressing

using of index sugister

# DEDICATED REGIGER ADDRESSING.

In dedicated register Addressing mode, the address of one of the operand is specifical by a dedicated RPV Register BMAR [ Block Move address register].

En another care of declicated register addressing on of the operand is the content of a dedicated on of register DBMR [ Dynamic Bit Manupulation Register]

Example:

BLDD BMAR Of h [The instruction will copy the Content of source address to distinction address]

The Source address is the content of BMAK.

The lower 8 bits of destination address is 6 Fh.

and upper 9 bits of destination address is the

Content of DP

# CIRCULAR ADDRESS MON:

The circular addressing is similar to the indirect addressing. This addressing mades allows the specified numbers buffer to be accessed sequently with a pointer that automatically wraps around to the beginning of the buffer when the last location is accessed

In order to hold the short and end add resses of the arcular briffin . DSP Processor has four sircular briffin snegister.

CBSR 1: Circular Buffer 1. Start Address Register CRSR 2: Circular Buffer 2. Star Address Register

CRER 1: Circulae Buffer 1. End Address Registe

CBER 2 : Circular Bufferz End Address Regites

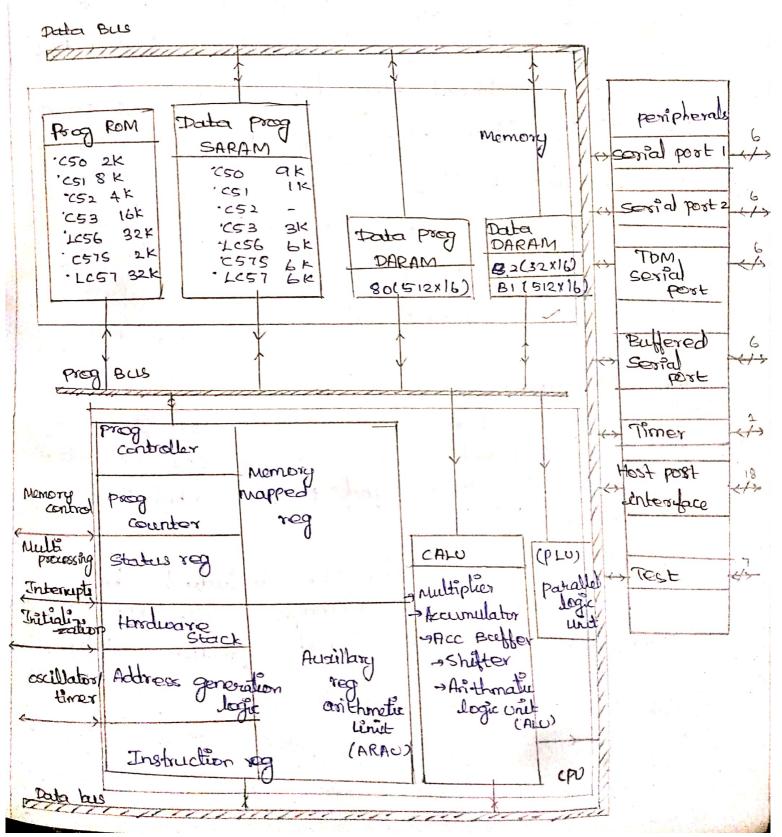

with sutable block diagram explain in detail about 6 [Nol Dec 201) TMS32064 DSP processon memory architecture 19ay / June 2014] Frehelecture of TMS 320057 JIAGI TEST program/bala Rom program/Dala Emulatim RAM control Program data Buses Buttered Soffal poxe-KemPT MAC ALU DMA TDM sortal 40 BIT ALU cho MXIJ MPN post ma CH-1 40 Bit adden chors operation Standard ¢h-2 sorial pour onspheral Exp Encodo DND, SAT MOST post CH-3 Accumulation Porter face (1+P2) Shubler Ch-4 Multchannel 40 bit 40 BIL ACCA Buttred Ch-5 porallel soral par 40 B9t ACCB (- lb131) PLI clean Addressing whit generator 8/w. d auxiliary regulates Walstate 2 addrossing cenit Oteneralsi power managementTMS320CF4 & a 16 69t fixed point degital signal procession.

It is Pabricated with an advanced modulised horvard archibeture that has one program memory bus, three data memory buses and Pour address buses.

Fasters processor family runs-160 MHZ with 1.6 volt Lowest voltage Remely runs-120 MHZ with 1.5 volt

### program bus:

From program memory.

CB, DB and EB Buses

It inters connects me copy relate address.

Generation legic, program address generation legic, on chip

Phoriphonals and data memory.

The fundinal black diagram of This 320 CF14 can be clivided into how see blacks. They one.

- 1) Internal memory organization

- 2) Contral processing and (cpu)

- 3) onchip phosphorau

Internal memory organisation

It is organized no three and indudly selectable spaces. They are

- \* Program

- \* Data

- The C54 devices can contain the bellowing

- \* Road only memory

- \* Pandom Acors momory

The PAM can derided anto inne type

- 1) Dual Acos PAM (DARAM)

- 2) Single Access DAM (SARAM)

- 3) Two way shored PAM

# Read only nemory (ROM)

\* It is part of the program momory space and 9n some cases parted of the data memory space and \* on most devices in the Rom winters a boot leader that B useful borr booting to faster on the or external PATA

### \* Dual Access PARA (DARAMA):

It is composed of several blocks. Each are accord twice per machine ayle.

The cpo and partiphenals can read from and curille to a DARAM monony address on the same yele. Single Access par C SARAM)

\* It is composed of several blocks. Each block so acceptable once per machine cycle for element o read or a wilter. It is always mapped in data space

Two way showd DAM:

The deries multiple op cores include two way

Shared RAM blocks.

All the showed memory is program wifle proletted or read my by the (pu only own concert memory access) and about con write to the shored memory.

2) central processing und cpv: It untains me bollowing famulin

- 1) multiply accumulate (MAC)

- 2) Anothometer Logge (unit (ALU)

- 3) shuften

- 4) Accumulators

- 5) Addressing unit

# Multiply Accumulate (MAC)

The Thes20054 include a 17161+ XIT bit multiplies a dedicated 40 bit odder bor non problemed mac operation.

The martiples supports signal signed multipleation. These operation allow extraction extended preatsion. airtimetic

Arithmatic Logic Unit:

It is implemented a wide scange of withmatic and logical functions, most of which execute in a single clock cycle.

After operation is performed in ALU, the result is usually transferred to destination

The ALU can also function as two separate 16 bit ALUS and perform two 16 bit operations simultaneously

ALU input constructed in two ways!

→ If 5 through o contain data memory operand then sa through 16 contain zero or signextended

and 29 through 32 contain either zero or sign extended.

### overflow Handling:

It am (overflow mode)=0, the accumulators one loaded with the Aw nesult without modification.

If orm = 1 the accumulator are loaded with most positive 32 bit value or most negative 32 bit Yalue depending on direction of overflow.

It can perform arithmetic & logical shifts by up to 31 bits Left or by up to 16 bit night Shiften 21/p Can come directly from data memory from either of two accumulator.

Shifter olp can be sent ALL or Stored in memory.

Accumulators: 31-16

AG AH

AG AH

Guard Bits

High order bits Low order bits

31-16

BG

BH

BL

Guardsits

High order bits

Low order bits

Accumulator A & B can be destination.

step ister for either the multiplier ladder unit or

the ALU.

Each accumulator is spilt into three parts. The quard bits are used as a head margin for Computations.

AG, AH, AL, BG, BH and BH one memory mapped register.

Addressing Unit:

The C54 DSP has three Status & logical registers: Status registers, Status registers, Status registers and processor mode Status

register (PMSR)

Sto and STI contain the status of Various condition and moder. PMSR contain memory Setup Status and control information.

6. Explain architecture of TMS320 C50 With next dig CMAY / JUNE 2013, NOV / DEC - 2010)

TM320050 digital signal processor is - fabricate With CMOS integrated cit technology.

It is a fixed point 16 bit processor running at 40 MHz. The single instruction execution times is 50 sec.

It's anichitectural design is based on combination of advanced Harvard architecture.

The functional block dig of tMS320C50 Car be divided into four Sub blocks

- -> Bus Structure

- topo (central processing unit)

- onchip Memory.

- onchip pheripherals

### Bus structure:

separate porgram & data buses in the advanced Harvasid architecture of C5x maximize the porocessing power and provide a high degree of parallelism.

In addition the CSX included the control mechanism to manage interupts, repeated operations and function calling.

The CSX auchitecture has four buses.

- priegram Bus (PB)

-> program Address Bus (PAB)

- Data readous (DAB)

program Beis: It carriers the instruction code and immediate operands from program memory of

program Address Bos: It provides address to program memory space for both read and Write.

\_ Data med Bus;

It unterconnect Various element of cpu to data memory space.

tata stead Address Bus:

It provides address to access the data memory space:

2) central processing Unit:

It consist of following elements,

- -> central Arithmatic Logic Unit (CALU)

- -> posalled logic Unit (PLU)

- Auxillary Register Arithmetic Unit (ARAU)

- 7 Memory Mapped Register

- -> program controller.

# central Arithmetic Logic Unit:

Complement arithmetic. It contain of following:

- -) lb bit x 16 bit porallel multipler

- -> 32 bit Acc buffer (AccB)

- product Register (PREGI)

- -> 32 bit accumulator (Acc)

- Additional shiptors.

The 16 x16 bit hardware multiplier is capable of computing a signed or un signed so bit product in single Machine

cycle.

The product register holds the product.

The 32 bit ALU and accumulator implement a Wide range of arithmatic & logic functions, the majority of Which execute is cycle.

one 31p to ALU comes from accumulator and other 31p can be accumulator and other 31p can be furnished from the product register to hultiplier, the accumulator buffer

(Acces) or olf of scaling shifter.

The result of operations performed in ALL Stored in accumulator.

that executes logic operations on data without affecting the contents of accumulators.

Auxillary Register Arithmatic Unit:

The CSx consists of siegister file containing eight auxillary register (ARD-ART) Each of 16 bit length, a 3 bit auxillary Each of 16 bit length, a 3 bit auxillary bit. ALU. The auxillary register file 9s connected to the auxillary register file 9s including those for CPU, Serial port, times and seftware Wait and State generator.

Program controller.

The pregram controller consist of logic circuitry that decodes the operiodical instructions, manages, the CPO pipeline, Stores the & Status of CPO operations and

the conditional operations. It consist of following elements,

- program counter

- -> Status and control Registers.

- -) Handwhere Stack

- Address generation logic

- Instruction register.

fregram Counter:

The CSX has a 16 bit program Counter(PC) which contains the address of Internal or external program memory used to fetch Instructions.

status and control Registers:

The C5x has foror status & Contral

Degister. They are,

- circular Buffer control Register

- Process mode status Register

- -> Status Register STO 8 STI.

circular Buffer control Register:

The Cox Control Lowo

Concurrent crocular Buffors.

-> CBSR1 & CBSR2 - Endicate When

circular Buffers Starts.

Scanned by CamScanner

CBERIA CBER? - Indicates When circular process made etatus buffer and.

Epace of data morrory page o and can be gaved in same way other does memory location.

Stadus register sto 8 STI:

It can be stored site date memory a loaded from date memory.

Hardware stack:

The 3s used an during interrupts

and subsoutine to 2000 2 restore the po

Address generation logic:

address bus is generated by the pregram counter when instruction & long immediate operands are accessed

# Instruction Register:

hold the opcode of the anstruction being executed.

a) on chip Memory: The Cox anchitecture has a total memory address range of 224x. Words x.16 bits. The memory space is divided into your memory segments. -> 64 k Word- program memory Space - 64 k Word - Local data Memory -164k Word- alp olp forts -) Bak Word - Global data Memory Space The large onchip Memory of CEX Includes, - program read only Memory - Data program single access RAM (SARAM) -> Data / program dual access RAM (DARAM) program read only Memory: of the cox DSP carry a 16 bit on thip maskable programmable ROM. - Mp/Mc 2s high for Microprocessor.

-, MP/Mc às down for Microcomputer. Data Program Dourd Access RAM: It can be configured in three Ways, - Data Momory - program Memory > Date and program Memory. Data/Program Dual Access RAM:

It can be configured in below: - Block o - stata and program memory -> Block 1 and Block 2 - Duta Memory. 4) onchip peripherals:-

clock generator:

When put option is selected, the cpu dock is multiplied by a specific factor and generators a low frequency clock than that of cpu.

Hardware timer:

The timer is on onchip down counter that can be used to

perdiocally generate cos interrupts. software programmable bait state It can extend external bus cycles up to seven Machine cycles. General puripose I/o pins: The C5x has two general purpose pairs that are software controlled. BIO- Mointers peripheral device Status. Via Soft Ware. familled I/o ports:

The CSX has 64 x parallel Ilo ports.

social port Interfaces; It consists of three different types of serial ports. They are, - General purpose Serial port. - Teme Devision Multiplexed Sexial

- Buffered Serial port.

### Buffered Serial port:

It is available on C56 & CS7 devices. It operates on either auto buffering or non buffering mode.

# Tom serial port:

It Is implemented on the (50, (51, and C53 devices. It operates in either TOM or non TOM mode.

# Host port Interface:

It 99 8 bit parallel Fort used to interface a host device or host processor to the CSX,

# User Markable Interrupts:

The csx has four external, maskable user interrupts that external devices can use to interrupt the Processor.

### Part-e

Operation of TMS32C50 proce81079

The bollowing society provides application oriented operation for

\* Modern application

\* Additive Pilleting

\* Inbonite - m. Impulse response (III) Albor

\* Dynamic programming

### Modern application

\* The CSX dovices with their enhanced installed set and reduced instruction each fine are particularly effective in implementing encoding and decoding algorithms

\* Teaches the circular addressing, repeat block and single cycle barried shift reduce the execution time of such reachers.

The defendant and convalutional encoder to a question both sound v. 32 modern was books coding with 32 carrier states

of the data stream to be cransmarted by data both.

The First 2 1973 9n 1970 "Oin and On in each group are determinally encoded into 4m and 12n according to the bollowing.

Yon = Qon + Yon-1 (4) Yon-1 (4) Qon

\* This is done by subsainte dett:

\* The two dubrentially encoded bits 4 in and 42n are used as propuls as to a conventional encodes substituting ENCODE, which generally a reclument bit 4 on. There Five bits one packed into a single word by the price substituting

### Adaptive Paltering

\* This is done by updating the coefficients and is consuming.

\* The MPYA, ZALD and PPTB Instruction on no est

\* Quantization emons in the updated coefficients can be minimized if the result is obtained by rounding rather than bruncating

\*The PFTB (repeat block) instruction allows the belock of instruction to be repeated without any pendly bor looping

\* The SARAM OF the & 5x can be modelfied in born me program and data spaces at me same how by setting the only and RAM associated floors of.

The coefficient table Is located on SARAM IST Is accessed by the MACD and Mpy instruction without modeling on RAM configuration.

# Infinite ampulse response (III Alter)

The Nth order IIP felter & represented by me bollowing two dubrence cautions.

At time enloyed n

you a the output of the IIR Palbr

$d(n) = x(n) - d(n-1)a_1 - \dots - d(n-N+1)a_{N-1}$   $y(n) = d(n)b_0 + d(n-1)b_1 + \dots + d(n-N+1)b_{N-1}$

\* The above equation is implemented on the C5x using the multiply -a cumulate instruction (MACI, MACI, MADI, MADI,

\* It also requires a data move operation to update the state variable sequence dans

### Dynamic programming

\* It is used Pri optional search algorithms

\* The apple after such as speach reagnition, telle communication and robotics used demance programming algorithms.

Scanned by CamScanner

- \*Most realitime seems algorithms used the basic dynamic programming, principle that the final ophimal first from the state to the goal state always passes through the an information of the passes through the an information of the passes that

- \* Identifying information patrix reduces a long time and the first god.

- \* AN Integral point ob any opinional secret scheme based on the dynamic programing pholiple is no back macking operation.

- \* From back hacking operation as necessary to the trace me operation pain when goal is nearned.

- \* The path history is stored in a circular butter butter butter butter butter butter butter butter butter between back tractures operation, the path hutory is updated by a sworch algorithm for the host time period.

- \* Each group of bour anseather memory location on the butter cornesponds to the expands of me bon pates by one nodo.

- \* Each element ob a group corresponds to one of the bour states in that time period

# 2) List out some of the application of This 320 pipes

### Automothe

- \* Adaptive orde control

- \* Angskied brakes

- \* collular telephones

- \* Digital radias

- \* Engine unhol

- \* Navigation and global positioning

- \* vebration analysis

- \* voga commands

- \* Anticollision radan

#### rusumen.

- \* Digital radios/TVs

- \* Educational toys

- \* Music synthesizes

- \* pagors

- y power look

#### control:

- Disk chave unno

- Laver part connol

- Robotta control

- servo conhol \*

- Motor control \*

# Graphics I maging

- \* 8D rolalim

- \* Animation | digital maps

- \* Image compression

- \* Image enhancement

- \* pattern reagration

# Industral:

- \* Numaric control

- \* power line monthoring

- \* Pobotics

- \* ecurity acos

### Medical

- \* piagnoza caupment

- \* Hearing aids

- \* ultra sound equipment

### Millay:

- \* Messle guidance

- \* Navigation

- \* Radan processing

- \* Radio Arequerry moderns, sensor

#### Voice speech

- \* speaker very fratten

- \* spean enhancement

- \* volce maet

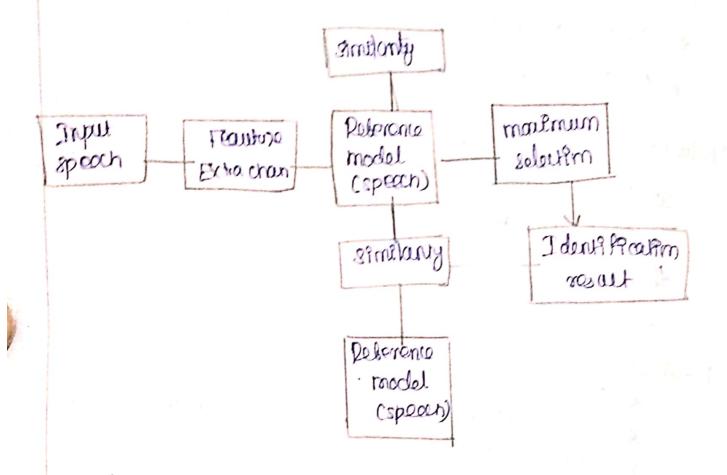

Feautine entraction is the process that entracts a small amount ob data from the voice signed that can later be used to represent each speaker

Feathers matching annothers the actual proadure to adouble the unknown speakers by companing extracted feathers from his her propert column the ones from a set of known speakers.

### Speach feauture Extraution:

convext the spean waveform to some type of parametric representation for further analysis and processing.

The specen signal is a slowly timed vonying signal.

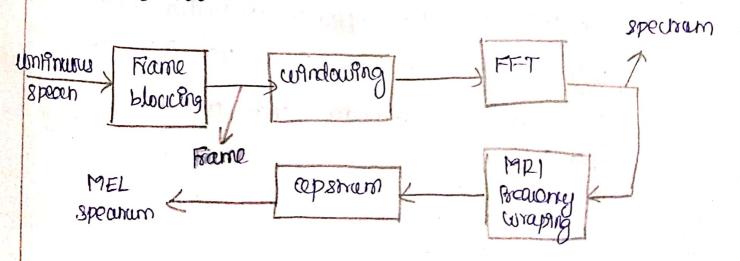

### MEL FREQUENCY CEPSTRUM COEFFICIENTS PROCESSOR

MFCC's one based on the known verfation of the human ears enflical bandwidths breaking and filter spaced linearity at low Are queries and logistimeterally at high Requestes have been used to capture the phonetically important chanalogistics of speech. The linear Are awany spacing below 1000 Hz and a logistimetic spacing

### FRAME BLOCKING:

\* confinuous speech signal is blocked into former ob N samples, with adjacent being separated by M. (MEN)

The 1975+ Prame consists of N samples second frame begins in samples above 1975+ Frame and overlap 19+ by 19-N samples

\* Third frame begins at 219 sample after Agros frames and 9t overlaps Pt by N-219 samples.

### Windowing

\* The nort step 9n the processing is to window each endividual hame so as to minemize. The signal disconfinedrous at the beginning and end of each of frame

\* to Friendeze the spectral destertion by using the window to abber the signal to zero at the boginnery and end of each fame

### Fast Arminer transform:

# It unvert can frame 66 N samples from the time domain and the frequency domain.

# The FFT B a fast algorithm implement the discrete frames transform (DFI)

### MEL Frequency wraping

The Mel Requency scale & lenear frequency spaceing below too Hz and a logisthmere scale above 1000 Hz apstrum:

- \* The log mel spectrum Is converted back to Ano

- \* The result is called the new frequency capstrum coefficients (MFCE)

- \* The apsnum representation of the speach speaking. provides a good representation of the signal broparties of the signal

### Feautive metantion Matching:

The feather matching techniques used in speaker recognition and added dynamic time the worping (DTOD), had den markov modelling (HMM) and vector quantization (VQ)